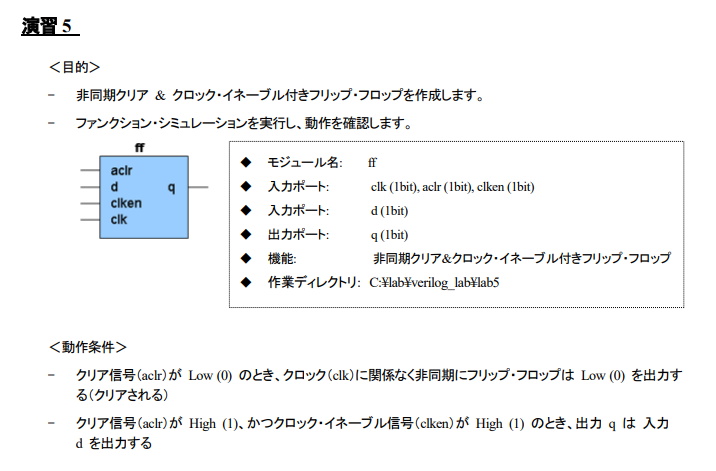

非同期クリア & クロック・イネーブル付きフリップ・フロップ

演習問題もいよいよ最後。。

フリップフロップ ってメモリなどに使われるデジタル回路の定番。

port map はこんな感じ

ff u1 (.aclr(aclr),.clk(clk),.clken(clken),.d(d),.q(q));

動作条件は

if aclr == 0 then q=0

if aclr == 1 & clken ==1 then q=d

って感じ

module ff ( input aclr,input clk,input clken,input d,output q);

reg q;

always @ (posedge clk)

case ({aclr,clken})

2'b00 : q <= 0;

2'b01 : q <= 0;

2'b10 : q <= 0;

2'b11 : q <= d;

default: q <= 0;

endcase

endmodule

かな?って書いてみたけど。。

非同期リセット付き

http://www.kumikomi.net/archives/2009/07/verilog_hdl.php?page=3

ここにあるように。。aclrが0になった瞬間に、clkと非同期に状態が変わらないといけないみたいなので。。

always @(posedge clk or negedge aclr)

としないといけないみたい。

とすると、条件分岐も

if (aclr == 1'b1) q<=1b'0; else if ( clken == 1'b1) q<=d;

って感じか。。

動かしたコードをGithubにおいておきました。

Githubの全体のリポジトリはこちら

https://github.com/tom2rd/VerilogHDL-Modelsim1

- 【FPGA】Intel/Altera DE10 standard メモ【リンク集】

- 【FPGA】ModelSimをちょこっと使ってみる チュートリアルの演習1まで【Verilog HDL】

- 【FPGA】Tutorial 演習問題を解きながら理解しようと。。演習2 4ビット乗算器【Verlog HDの基礎の基礎】

- 【FPGA】Tutorial 演習問題を解きながら理解しようと。。演習3マルチプレクサ【Verlog HDの基礎の基礎】

- 【FPGA】ModelSimのTutorial 。。演習4 7セグ・デコーダ【Verlog HDの基礎の基礎】

- 【FPGA】ModelSimのTutorial 。。演習5 非同期クリア & クロック・イネーブル付きフリップ・フロップ【Verlog HDの基礎の基礎】

とりあえず、Verilog HDLの練習は、ここまでとしよう。。次はいよいよ。。FPGAに焼いてみるところかな??

本HPのFPGA関係は、こちら

コメントを残していただけるとありがたいです