目次

タイミングシミュレーション??

FPGAの資料ってたくさんWebにあるけど。。読むのがメンドクサイ上に、VerUpが頻繁なようで、なかなかやりたいことや、初めにするところにたどりつかない(笑)。。

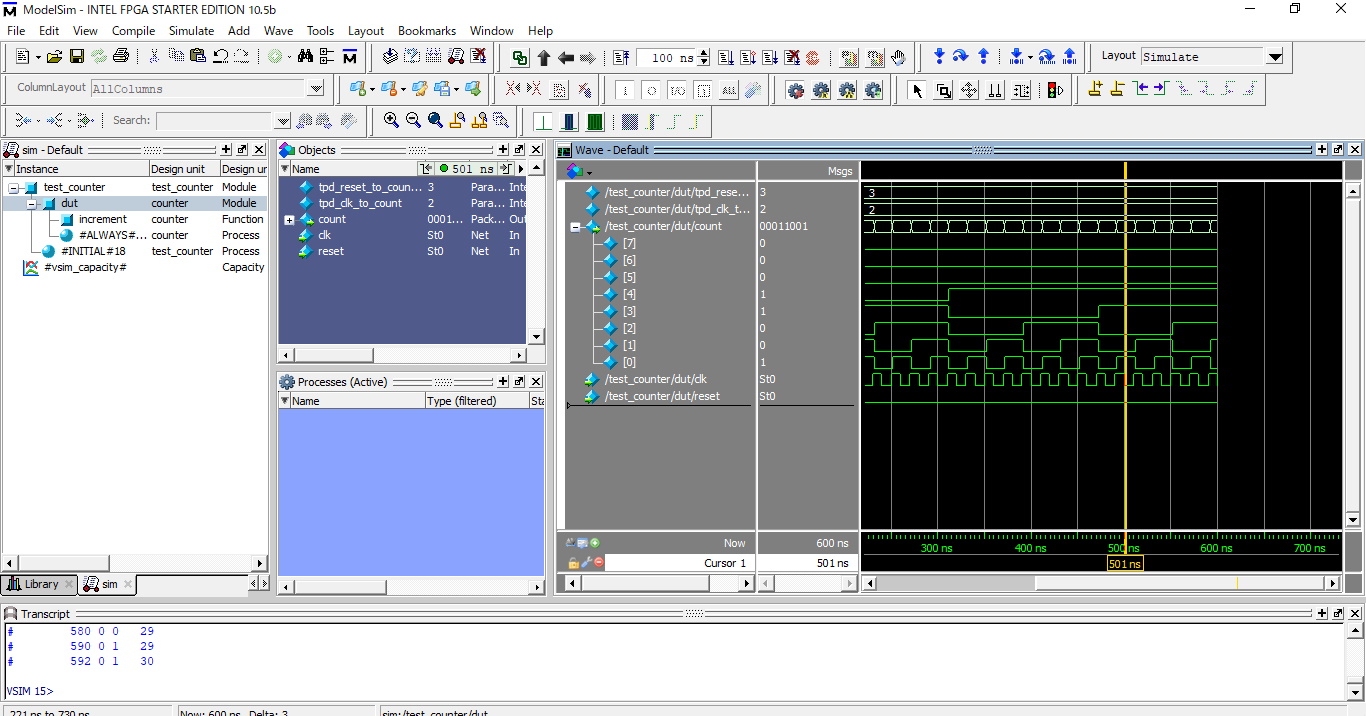

で。。SampleやTutorialがついているModelSimをちょこっと動かしてみようかと。。

https://blog.tiqwab.com/2018/03/25/get-started-with-modelsim.html

を参考にはじめてみました。

ModelSimのGUIを使ったTutorial

その前に、こちらで、Tutorialを動かして、だいたいのModelSimの動きを体感しておくのがいいです。

この通りやると Verilog HDLをコンパイルしてSimulationして波形まで出せます。

ちなみに、TutorialやExampleには、counter と PLIを使った Fibonacci, Transverse_designっていうのが入っています(ModelSimのディレクトリ内)

FPGAのプログラミングってちょっと甘く見てました(笑)専門用語多すぎ。。

モジュールとテストベンチの作成

- Verilog-HDL 入門

- Verilog HDLをマスターしよう!!(Monoist)

- はじめてみよう!テストベンチ Verilog HDL 編(macnica)

- はじめてみよう!Verilog-HDL <演習問題つき>

これにMacnicaの資料に演習問題がついているんですが。。。。基本の概要みたいなのが理解できてないときついですね。。 あちこちある資料をざ~っといろいろ眺めてみます。。

設計・プログラミングの手順

RTL:Resister Transfer Level レジスタ転送レベル

レジスタ転送レベル(レジスタてんそうレベル、英: register transfer level、RTL)は、論理回路の動作記述などにおいて、「ゲートレベル」よりも一段抽象的な記述レベルである。ゲートレベルでは、組合せ論理回路の(すなわち、状態を持たない)ゲートのネットリストを記述するが、レジスタ転送レベルでは、状態を持つラッチ回路など順序回路に相当する最小の部分を「レジスタ」として抽象化(ブラックボックス化)する。その上で、論理回路の動作を、レジスタからレジスタへの転送と、(その転送中に組合せ論理回路を通すことで行われる)論理演算の組み合わせとして記述する。

Verilog HDLの基本

書式のルール

- ステートメント

- セミコロン ; 終了につける

- begin -end ステートメントが複数になる場合

- インデント付き改行 複数行でかける インデントは半角スペースかタブ

- コメント

- // コメント行

- /* */ 複数行コメント

- アルファベットの大文字と小文字を区別

- 数値表現・文字列のルール

あとは、触って覚えますかね??(笑)

モジュール が あってテストベンチがあって、Verilog HDLで書く。

プロジェクト作って、コンパイルして、波形を見るってところまでを自分でするのこんなにハードル高いんだ(笑)FPGLまだまだだな。。って思いながらも。。

演習問題のファイル

Verilog-HDL_Trial_Lab-Manual_r1__1.pdf

Verilog-HDL_Trial_Lab_r1_download__2.zip

演習問題の答えがないので。。それだけ入れておきますかね? Githubに入れるようにしていきます。

演習1

assign文

- ワイヤ同士をつなげたい場合

- sum を a と bにつなげます

module adder (a, b, sum); input [15:0] a, b; output [15:0] sum; assign sum = a + b; endmodule

演習2

always文

- あるタイミングで処理を起こしたい場合

- ループと同じ

assign文・always文とwire・regでの変数

wireで定義する変数 ネット型変数の信号への代入は,assign 文でのみ可能。

regで定義する変数 レジスタ変数の信号への代入は,always 文,initial 文,task,function の中で可能。

つまり,reg =順序回路という訳ではなく,wire や reg は上記の文法的な理由で使い分ける,と理解しておいて間違いなさそうです。いずれの変数も,式の右辺や引数としての利用(値を参照する場合)は可能。

あんまり長くなってきたので。。 ページ分けて書くことにしますね・・

コメントを残していただけるとありがたいです