これまでの経緯

全部書くのメンドクサイので、前回は、

【FPGA】Tutorial 演習問題を解きながら理解しようと。。演習3マルチプレクサ【Verlog HDの基礎の基礎】

でした。 続いて 演習4です

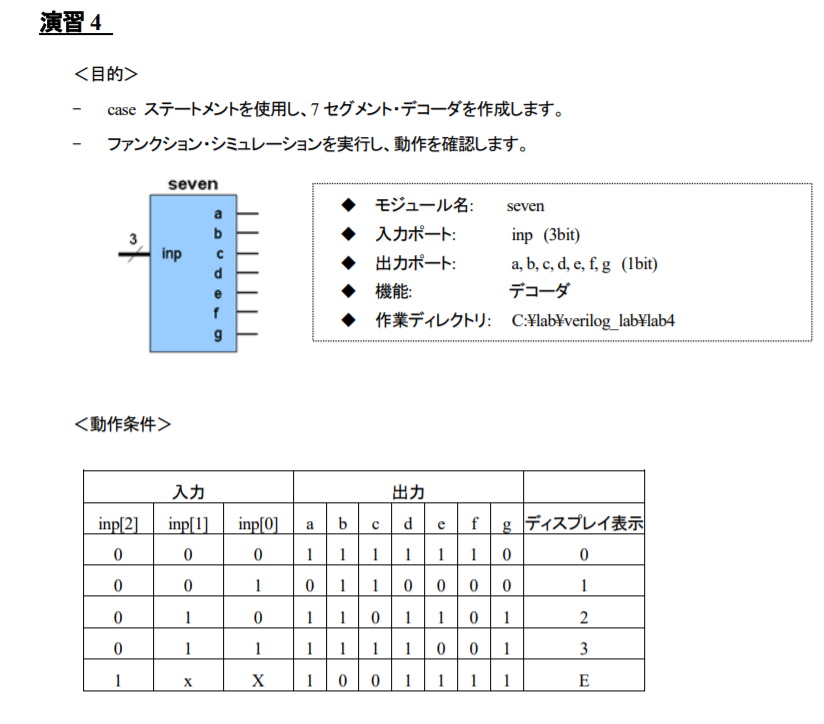

演習4 7セグ・デコーダ

Case を使って、入力 inp3ビット から、a,b,c,d,e,f,g に 1ビットづつ出力しろと。。

7セグデコーダのサンプルもググると沢山でてきますね。

http://www.arch.cs.kumamoto-u.ac.jp/project/kite/3days/explain/VHDL/example/7segment_decoder.html

https://www.fpga4student.com/2017/09/seven-segment-led-display-controller-basys3-fpga.html

テストベンチを見てみる。。ピンを配列化?

Portmapの記述が、こんな感じ

seven u1 (.inp(inp),.a(a),.b(b),.c(c),.d(d),.e(e),.f(f),.g(g));

出力a,b,c,d,e,f,g がばらばらになっているので。。 書き方としてなんか工夫ないかな?って調べてたら。。

http://ifdl.jp/akita/class10/2.html

に、Encoder Decoderで 配列のような扱い方が書かれていました。

module sample(SW, LED);

input [1:0] SW;

output [3:0] LED;

wire [1:0] d;

reg [3:0] q;

assign d = {SW[1], SW[0]};

assign LED = q;

always @(d) begin

case (d)

2'b00 : q <= 4'b0001;

2'b01 : q <= 4'b0010;

2'b10 : q <= 4'b0100;

2'b11 : q <= 4'b1000;

endcase

end

endmodule

このVerilog HDL簡易文書法だと、case内で{a,b,c..}みたいな使い方もできるみたいですね。

いったん、7ビット幅の配列にして、assign すれば良さそう。

reg[6:0] outseg ;

assign outseg={a,b,c,d,e,f,g};

って感じかな?

こういう書き方をしておくと、case 内での書き方がきれいになりそうですね。

上の動作条件を一応書いてみると

always @(inp) begin case (inp) 3'b000: outseg<= 7'b1111110; 3'b001: outseg<= 7'b0110000; 3'b010: outseg<= 7'b1101101; 3'b011: outseg<= 7'b1111001; 3'b1xX: outseg<= 7'b1001111; endcase end

ん?? x?? 不定って表せるのかな??

やってみますかね??

regにイコールで代入できない。。そうだよね。assignも反対だし。。ということで。。

module seven(inp, a,b,c,d,e,f,g); input[2:0] inp; output[1:0] a,b,c,d,e,f,g; wire[2:0] inp; reg[6:0] outseg; assign a=outseg[6]; assign b=outseg[5]; assign c=outseg[4]; assign d=outseg[3]; assign e=outseg[2]; assign f=outseg[1]; assign g=outseg[0]; always @(inp) begin case (inp) 3'b000: outseg<= 7'b1111110; 3'b001: outseg<= 7'b0110000; 3'b010: outseg<= 7'b1101101; 3'b011: outseg<= 7'b1111001; 3'b1XX: outseg<= 7'b1001111; endcase end

とりあえず、これで動いたけど、やっぱり3’b1XX ってうまく動かないみたい。

論理値

(2) 論理値

1ビットの信号が取りうる値は,論理回路の世界では0と1ですが,VHDLの世界ではこれだけではありません.不定値Xや,ハイ・インピーダンスのZがあります.正確に言えば,これら論理値もパッケージの中で定義されています.(出典)

X:不定値

Case 文と ?X Zの補足文

http://zakii.la.coocan.jp/hdl/59a_zx_compare.htm

?と書けばいいのか?

あと、Caseにはdefault って書くときとOthersと書くときがあるみたいだけど。。どっちなのかな??

default: outseg<=7'b1001111;

とりあえず、これを入れたら。。思い通りの結果にはなったけど。。

3’b1??: outseg<= 7’b1001111; でも XXでも動くので。。どっちが正解か??わからないです。。誰か教えて~

Githubにソースおいておきます。

ちなみに、Case文はこちらも参考に

http://hirokinakaharaoboe.net/yaruo_verilog/chapter1_7.html

コメントを残していただけるとありがたいです