知らないこと勉強するのって。。面白い

こんな年で、こんなことするのって。。意外に面白いですね。。まぁ、大学生の学部レベルの話だからなんだろうけど(笑)

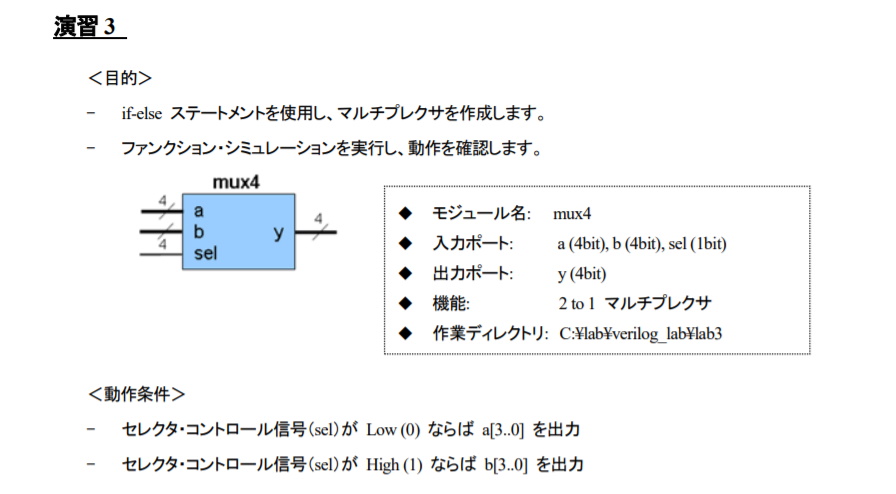

演習3 マルチプレクサ

Multiplexerは、ググると沢山でてきます。これも表現方法いろいろあるんですね。

https://www.chipverify.com/verilog/verilog-4to1-mux

http://electrosofts.com/verilog/mux.html

https://github.com/Obijuan/open-fpga-verilog-tutorial/wiki/Chapter-11:-2-to-1-multiplexor

https://qiita.com/rikitoro@github/items/ab3a734b4e19df0ad19f

if elseで書けという指示。。

module mux4( sel, a, b ,y); input[1:0] sel; input[3:0] a; input[3:0] b; output y; reg y; wire[1:0] sel; wire[3:0] a; wire[3:0] b; always @( sel or a ) begin if( sel == 0) y = a; if( sel == 1) y = b; end endmodule

こんな感じ??

elseを使うと

module mux4( input wire sel, input wire [3:0] a, input wire [3:0] b, output reg [3:0] y ); always @ (*) begin if (sel) begin // selが非0の場合が成立, 0の場合が不成立 y = a; // selが成立のとき、こちらが実行される end else begin y = b; // selが不成立のとき、こちらが実行される end end endmodule

コピペを改変ですが。。

こんなのかな?

ちゃんとテストベッド見よう(笑)

Tutorialの演習3 Verilog-HDL_Trial_Lab_r1_download__2.zip

結果は、こちら

Selが1の時 a で 0の時 bになってますね。

コメントを残していただけるとありがたいです